1. 설계할 프로세서 구조 선정

컴퓨터는 크게 Input, Output, Memory, Datapath, Control이라는 5가지 구성 요소로 이루어져 있다. Datapath와 Control을 합쳐 Processor라고 부르며, 우리는 앞으로 processor의 구성(설계)을 공부할 것이다.

기본적으로 CPU time = Instruction Count x CPI x Cycle time이며, 프로세서 설계의 영향을 받는 것은 CPi와 cycle time이다. 따라서 프로세서 설계를 시작할 때에는 CPI와 cycle time이 어떻게 결정될 것인지를 우선적으로 제시해야 한다. 본 글에서는 단일 clock cycle에 단일 명령어의 수행 시작부터 끝까지에 해당하는 single-cycle processor를 설계할 것이며, One instruction per cycle(CPI = 1)이며 Cycle time은 동작이 가장 긴 명령어에 의해 결정될 예정이다. CPI가 1인 상황은 가장 간단한 상황이며, Cycle time 설정 방식은 cycle time이 길어질 수 있으므로 그닥 좋은 설계 방식은 아니다.

또한 MIPS ISA의 명령어들 중 일부분인 lw, sw, add, sub, and, or, slt, beq만 지원할 것이다. 그런 후 unconditional jump 명령어 중 하나인 j를 추가적으로 구현할 것이다. floating-point 명령어를 제외한 모든 명령어 및 포맷을 다룰 예정이다.

2. Logic design

프로세서의 설계는 [1] Datapath를 설계한 후, [2] Control을 설계하는 순서로 이루어진다. 이들은 모두 digital logic이므로 이에 대한 복습이 당연히 필요하다.

(1) Combinational and Sequential

프로세서의 logic element들은 크게 2가지 타입으로 구분될 수 있다. [1] Combinational elements는 Data value에 operation을 수행하는 요소이고, 출력은 현재의 입력에 의해서만 결정된다. 즉, 입력이 같으면 항상 같은 출력을 도출한다. 피드백 경로가 존재하면 안 되는 구조다. ALU, multiplexer, decoder, encoder 등이 이에 해당된다. [2] State elements는 State를 저장하는 요소다. 일반적으로 clock이 입력으로 사용된다. 특정 조건이 만족하는 경우에만 state element가 업데이트되는 상황이라면, write enable로 사용되는 control signals이 존재한다.

Combinational circuits는 Combinational elements들로만 구성된 논리 회로다. 출력은 현재의 입력에 의해서만 결정된다. Sequential circuits는 state elements로만 구성되거나, state elements와 combinational elements로 구성된 논리회로다. 일반적으로 combinational logic의 입력은 state elements로부터 오며, combinational logic의 출력은 다시 state elements의 입력으로 사용되는 형태다. 즉, 출력은 현재의 입력과 현재의 상태에 의해서 결정된다. 이 경우, Feedback path가 허용된다.

(2) Clocking methodology

Clocks는 state elements가 언제 업데이트되는지를 결정하며, Sequential logic circuit에는 반드시 존재한다. Clocking methodology는 clock과 관련하여 state change가 언제 일어나는지를 결정한다. 2가지가 존재하며 [1] Level-sensitive clocking methodology란 state change가 clock의 특정 level에서 이루어지는 경우를 말한다. Latch가 주요 예시라고 볼 수 있다. [2] Edge-triggered clocking methodology란 state change가 clock edge에서 이루어지는 경우를 말한다. Rising(positive) edge 또는 Falling(negative) edge가 사용된다. 이러한 clock edge들은 state element의 입력이 state element로 쓰여지도록 하는? Sampling signal로 사용된다. Flip-flop가 주요 예시라고 볼 수 있으며, [1]보다 사용하기도 설명하기도 더 간단하다.

-> 앞으로의 글에서 일반적으로 clock signal을 따로 표시하지 않기로 한다. 모든 state element들은 동일한 clock signal을 사용한다고 가정하며, 일반적인 설계에선 표시하지 말자.

Edge-Triggered Clocking을 사용한 Sequential circuit의 예시를 보자. p13~14 참고

Sequential circuits에서는 아래와 같은 feedback이 허용된다. (물론 아래의 경우, reset 또는 preset logic도 필요하다.) Feedback Path가 있더라도 state element는 clock을 사용하여 feedback을 일정 기간 막아준다. 동일 시간 대의 즉각적인 피드백이 없으므로 회로의 안전성이 유지된다. 반면, Combinational circuit의 경우 피드백 경로가 허용되지 않는다.

(3) Signal 관련 용어들

[1] Control signal이란 Multiplexer에서 입력을 선택하거나, functional unit의 동작을 지시하는데 사용되는 신호다. [2] Data signal이란 Functional unit에 의해서 처리되는 정보를 담고 있는 신호다. [3] Bus란 단일 logic signal로 취급되는 signal line들의 묶음이다. 단일 signal line보다 두껍게 표시되며, signal line의 개수도 같이 표현할 수 있다. [4] Asserted란 신호가 logically high(active)인 상태를 의미하고, Deasserted란 신호가 logically low(inactive)인 상태를 의미한다.

(4) Logic elements

[1] Multiplexer(Mux)란 Control signal에 따라 여러 입력들 중에 1개를 선택하여 출력으로 내보낸다. Selector라고도 한다. 다양한 데이터 입력 수에 대한 MUX가 존재하며, N개의 입력에 대해서는 [log2N-bit] selector signal이 필요하다.

참고로, Logic Elements의 Array는 아래와 같다. 32-bit wide MUX는 실제로 32개의 1-bit MUX들로 이루어진 배열이며, 이러한 배열은 다양한 logic element에 적용될 수 있다.

[2] Latch란 내부에 저장된 상태를 출력으로 내보내는 state element다. Clock이 asserted되어 있는 동안, 입력이 변할 때마다 상태가 변경된다. 즉, Level-sensitive이며, Active high 또는 Active low다. 이 중에서도 D latch(transparent latch)란 Clock이 asserted되어 있는 동안, 입력 신호의 값을 내부 state에 저장하는 latch다.

[3] Flip-Flop이란 내부에 저장된 state를 출력으로 내보내는 state element이다. Clock edge에서만 state change가 일어난다. Edge-sensitive이며, Rising edge 또는 falling edge다. D flip-flop은 Clock edge에서 입력 신호의 값을 내부 state에 저장하는 flip-flop으로, 간단하게 2개의 D latch들로 구성된다.

해당 강의에서는 edge-triggered clocking methodology를 사용하므로, D flip-flop으로 만들어진 레지스터들을 사용한다. 이는 n-bit 입력 및 n-bit 출력을 가지며, Clock signal은 입력값이 레지스터에 언제 작성되는지를 결정한다. 또한 매 clock cycle마다 레지스터에 입력이 작성되는 것이 아니라, 특정 조건이 만족할 경우에만 레지스터 값이 변하게 하고 싶다면 write enable로 사용되는 control signals가 필요하다. 해당 신호가 asserted된 경우에만, 다음 clock edge에서 입력이 레지스터에 저장된다. deasserted된 경우엔 레지스터 값의 변화가 없는 셈이다.

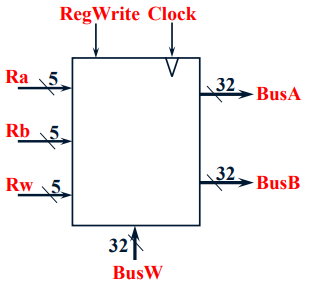

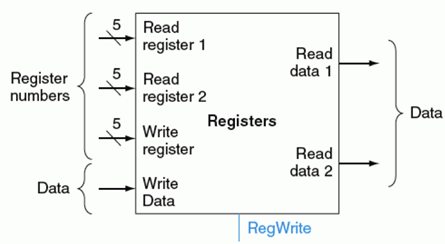

Resister file이란 레지스터의 집합으로, 레지스터 넘버를 지정하여 특정 레지스터의 값을 read or 특정 레지스터의 값에 write한다. 우리가 사용할 Resister file은 Two read ports and one write port를 가진다. 명령어 당 이 값들이 최대이며, R-format 명령어를 사용 가능하다. [1] Read할 경우, 2개의 레지스터 넘버(5-bit inputs)와 2개의 출력(32-bit outputs)이 필요하다. 즉 Read operation은 enable 또는 clock signal과 관련없이 항상 지정된 레지스터의 값을 Bus로 출력한다. [2] Write할 경우, 1개의 레지스터 넘버(5-bit inputs)와 1개의 출력(32-bit outputs)과 1개의 Write enable(1-bit input)과 Clock이 필요하다.

아래의 Symbol을 보자. BusA, BusB는 각각 레지스터에서 읽어진 데이터들의 출력 버스들이다. BusW는 레지스터에 쓰여질 데이터를 캐리하는 입력 버스다. Ra, Rb는 각각 BusA, BusB들로부터 읽어온 레지스터 넘버이고, Rw는 BusW에 쓰여질 레지스터 넘버다. RegWrite는 write enable이다.

메모리(Memory)도 살펴보자. p25

(5) ALU design

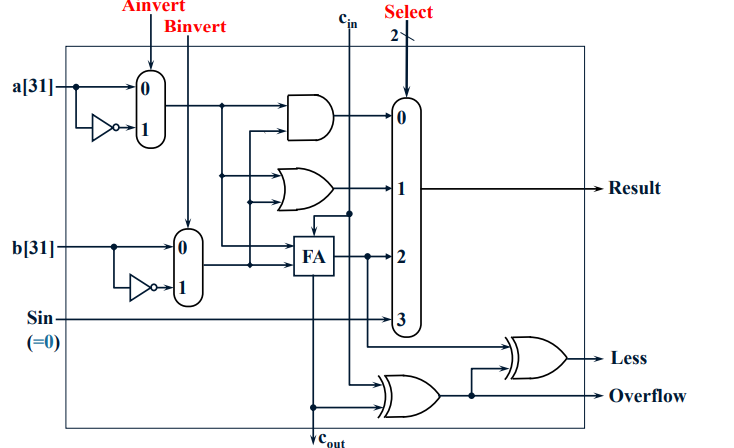

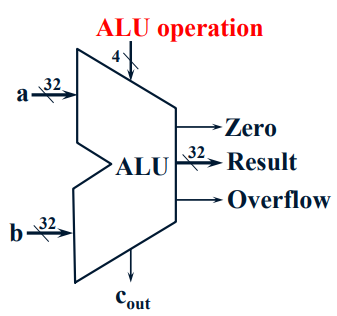

ALU에는 AND, OR NOR, add, subtract, slt, Carry, Overflow, Zero 등의 operation들이 들어갈 것이다.

| Select | Ainvert | Binvert | 결과 |

| 00 | 0 | 0 | a AND b |

| 01 | 0 | 0 | a OR b |

| 00 | 1 | 1 | a NOR b |

| 10 | 0 | 0 | a + b |

| 10 | 0 | 1 | a - b |

| 11 | 0 | 1 | set on less than |

이를 요약하여 그리면, 아래와 같은 그림이 나온다.

| ALU operation = {Ainvert, Binvert, Select} |

Function |

| 0000 | AND |

| 0001 | OR |

| 0010 | add |

| 0110 | subtract |

| 0111 | set on less than |

| 1100 | NOR |

3. Single-cycle procdessor implementation

(1) Datapath

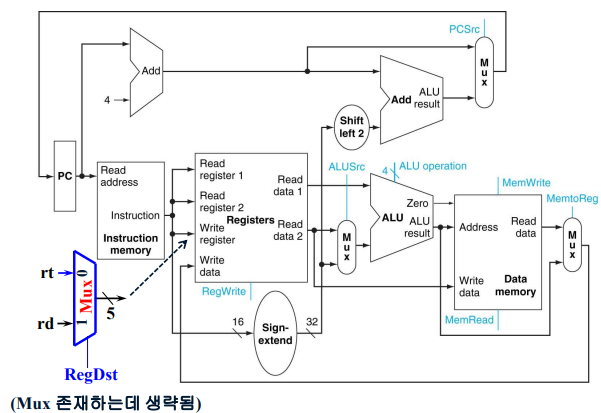

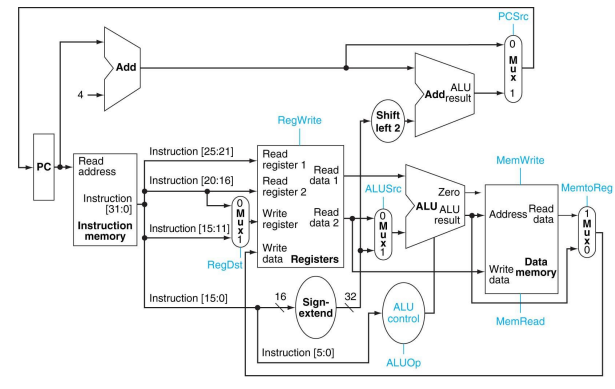

Datapath를 전부 구성하면, 아래와 같이 설계된다.

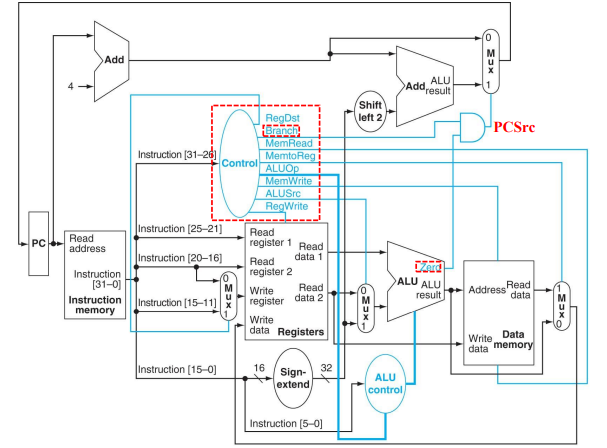

(2) Control

Main control, ALU control 등을 전부 구성하면, 아래와 같이 설계된다.

참고로, Main control은 총 7개로, ALUOp 안에 다 집어넣어 설계한다.

| Main control | deasserted( = 0 ) | asserted( =1 ) |

| RegDst | Register destination number = rd (instruction bits 20:16) |

Register destination number = rd (instruction bits 15:11) |

| RegWrite | None | 지정된 레지스터에 register write data를 write |

| ALUSrc | 2nd ALU operand = second register file read data |

2nd ALU operand = 명령어의 sign-extended 16 lower bits |

| PCSrc | Next PC = current PC + 4 | Next PC = branch target |

| MemRead | None | 주소에 의해 지정된 메모리의 데이터가 RData로 read됨 |

| MemWrite | None | 주소에 의해 지정된 메모리에 WDtata를 write함 |

| MemtoReg | Register write data = ALU output | Register write data = RData |

| Main Control Signals | R-format | lw | sw | beg |

| RegDst | 1 | 0 | X | X |

| ALUSrc | 0 | 1 | 1 | 0 |

| MemtoReg | 0 | 1 | X | X |

| RegWrite | 1 | 1 | 0 | 0 |

| MemRead | 0 | 1 | 0 | 0 |

| MemWrite | 0 | 0 | 1 | 0 |

| Branch | 0 | 0 | 0 | 1 |

| ALUOp1 | 1 | 0 | 0 | 0 |

| ALUOp0 | 0 | 0 | 0 | 1 |

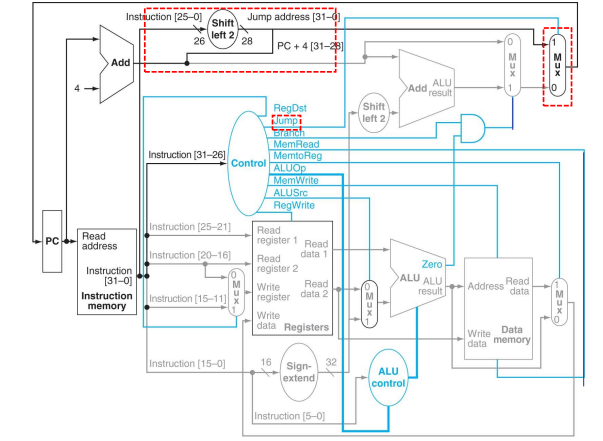

(3) Jump Instruction

Jump Instruction을 추가하면, 아래와 같이 설계된다.

(4) Single-Cycle Machine의 Cycle Time

내용 ~~

'KNU_study > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조(6) Processor : Pipelined Implementation (1) | 2023.12.30 |

|---|---|

| 컴퓨터구조(5) Processor : Pipelined Implementation (1) | 2023.12.22 |

| 컴퓨터구조(3) Computer Arithmetic (1) | 2023.12.22 |

| 컴퓨터구조(1) Software and hardware of computers (1) | 2023.10.26 |