이전 글의 개념(38디코더를 사용하는 이유)이 필요하다면 여기를 클릭 !!

example problem

<예제 1>

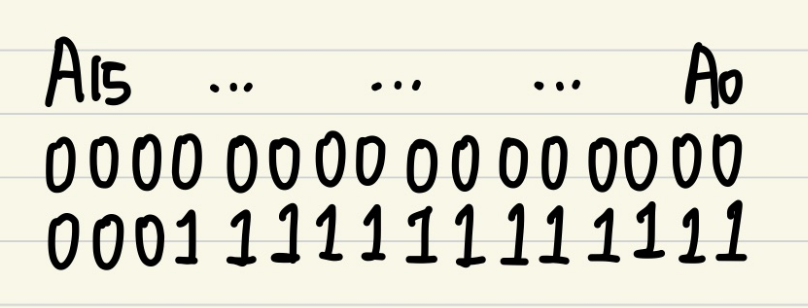

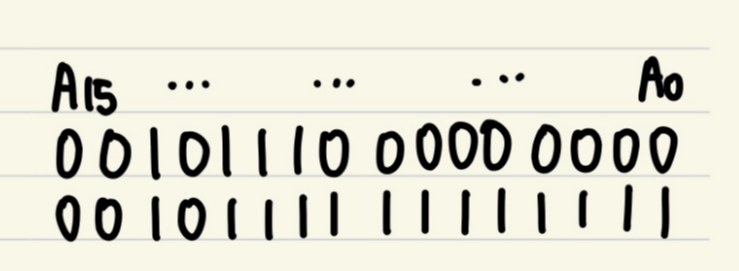

0000H ~ 1FFFH 메모리를 설계하시오. (38 디코더를 사용)

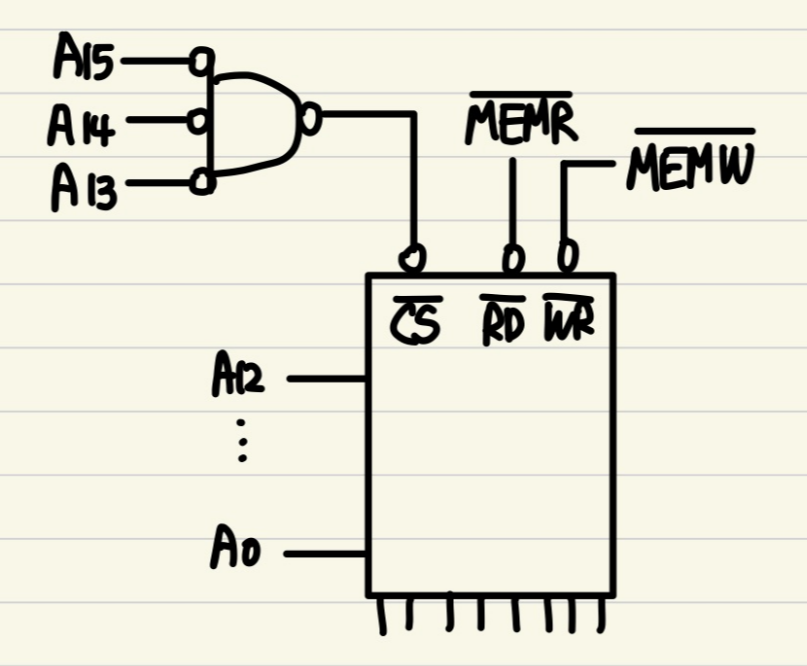

처음 주소와 끝 주소를 비교하였을 때, A15부터 같은 값을 가지는 bit까지를 CS에 연결한다.

-> 남은 값들은 address bus로 할당한다.

또한 NAND 대신, decoder를 사용할 수 있다.

-> 38디코더 : 같은 크기의 메모리 8개까지 확장 가능

-> 하 실수를 또 했넹.. E1과 E2위에 바(bar)가 있어야 하고, E3위엔 아무것도 없어야 합니다!!

<예제 1-1>

예제1 보다 1 큰 번지를 할당하였을 때, 해당 메모리의 시작 번지와 끝 번지는 ? + 설계해라.

-> E1과 E2위에 바(bar)가 있어야 하고, E3위엔 아무것도 없어야 합니다!!

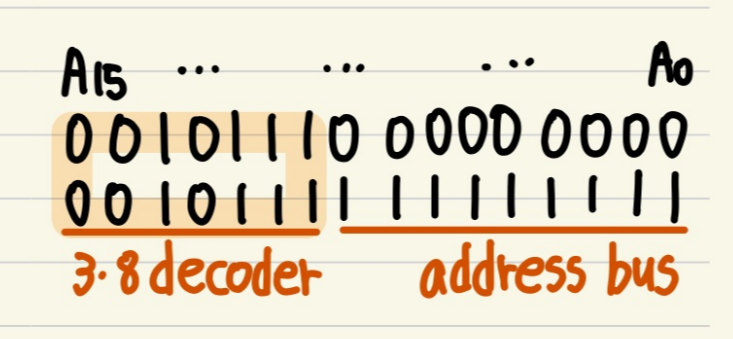

<예제 2>

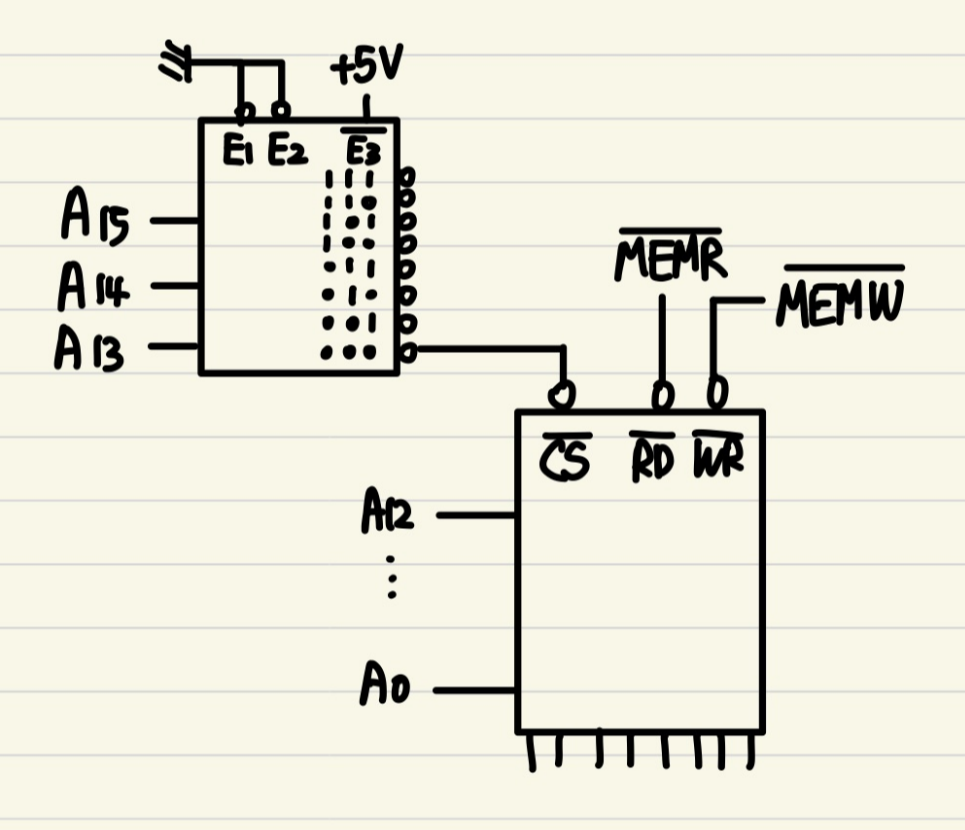

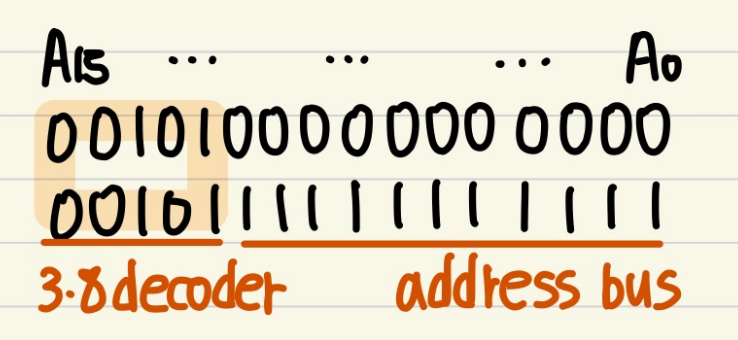

2800H ~ 2FFFH 메모리를 설계하시오. (38 디코더를 사용)

-> 38 디코더라서 3개만 디코더에 달아준다.

-> 나머지 A14, A15는 E1바에 달아줘도 디코더는 바르게 동작한다.

-> 대신 Mirror memory가 발생한다. Mirror memory를 모른다면 여기를 클릭 !!

<예제 3>

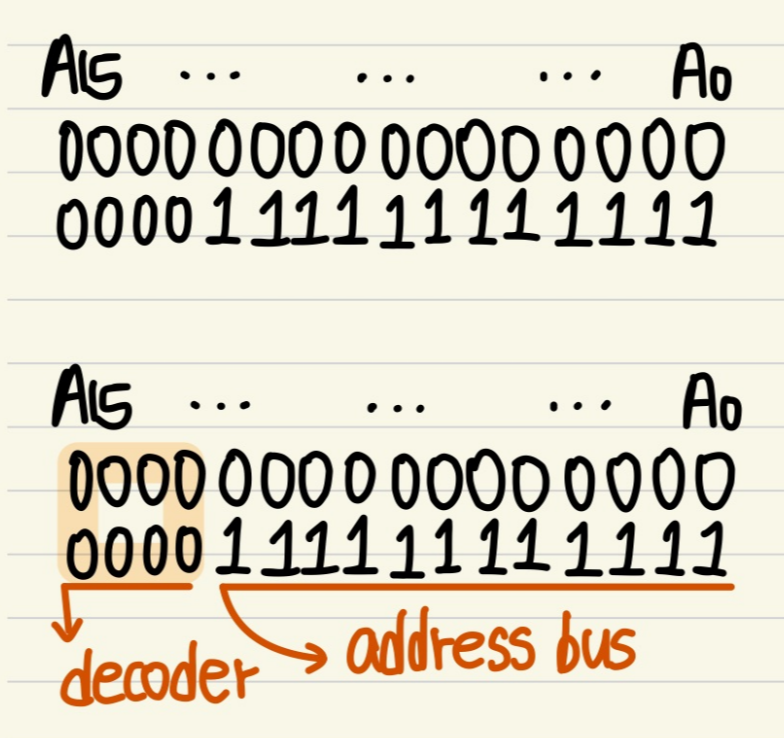

2E00H ~ 2FFFH 메모리를 설계하시오. (38 디코더를 사용)

-> NAND gate를 이용하여 mirror memory가 될 값들을 연달아 달아놓는다.

-> A15 ~ A12가 0010이므로 필요에 따라 inverter를 붙여준다.

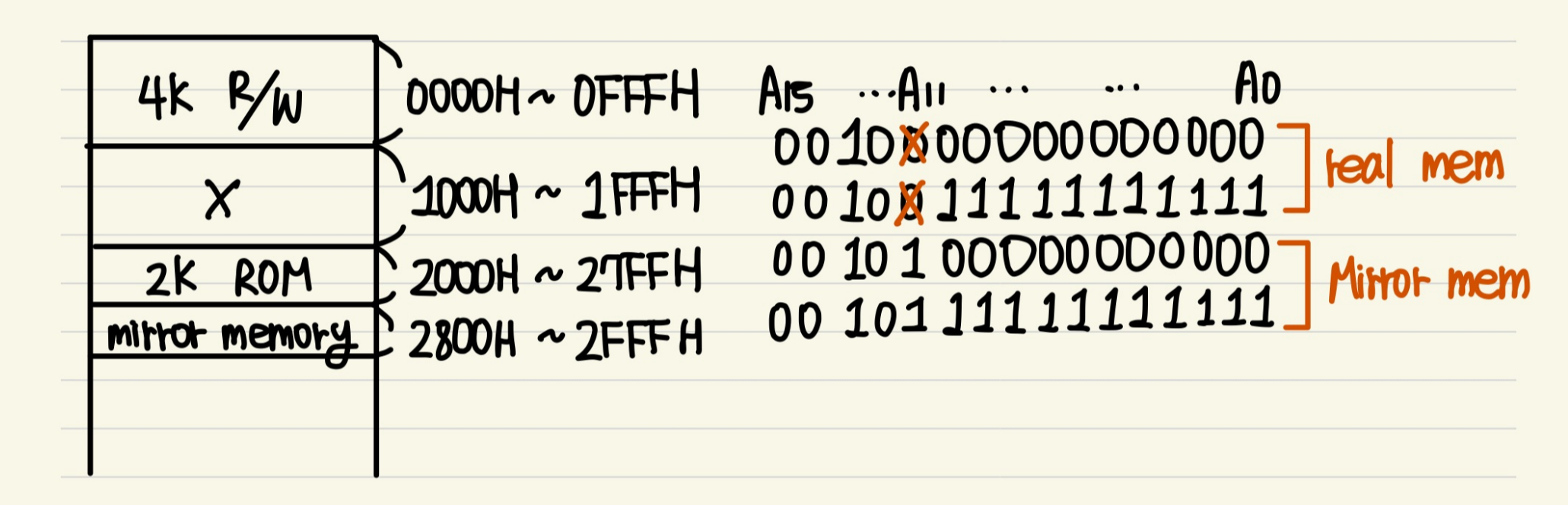

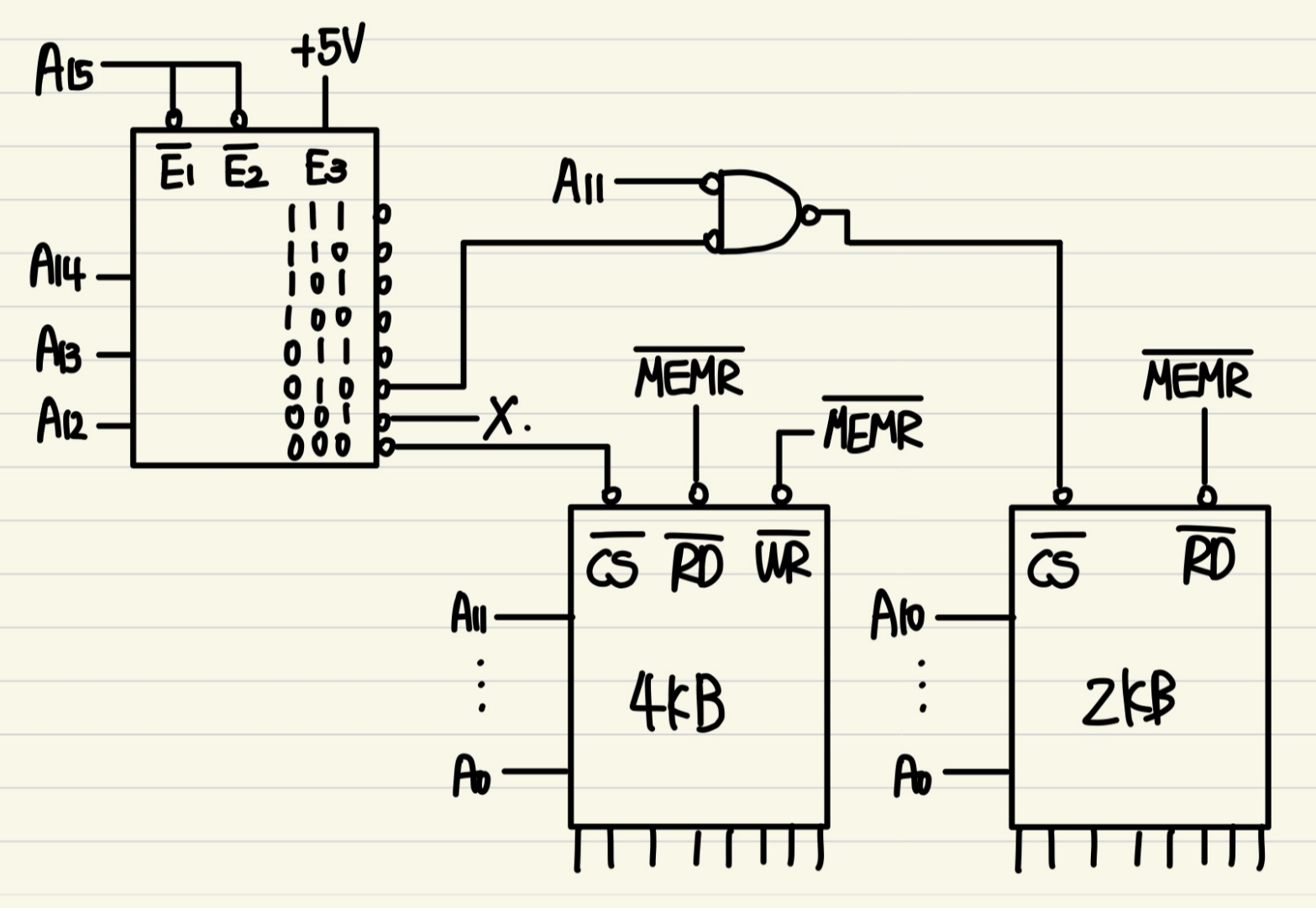

<예제 4>

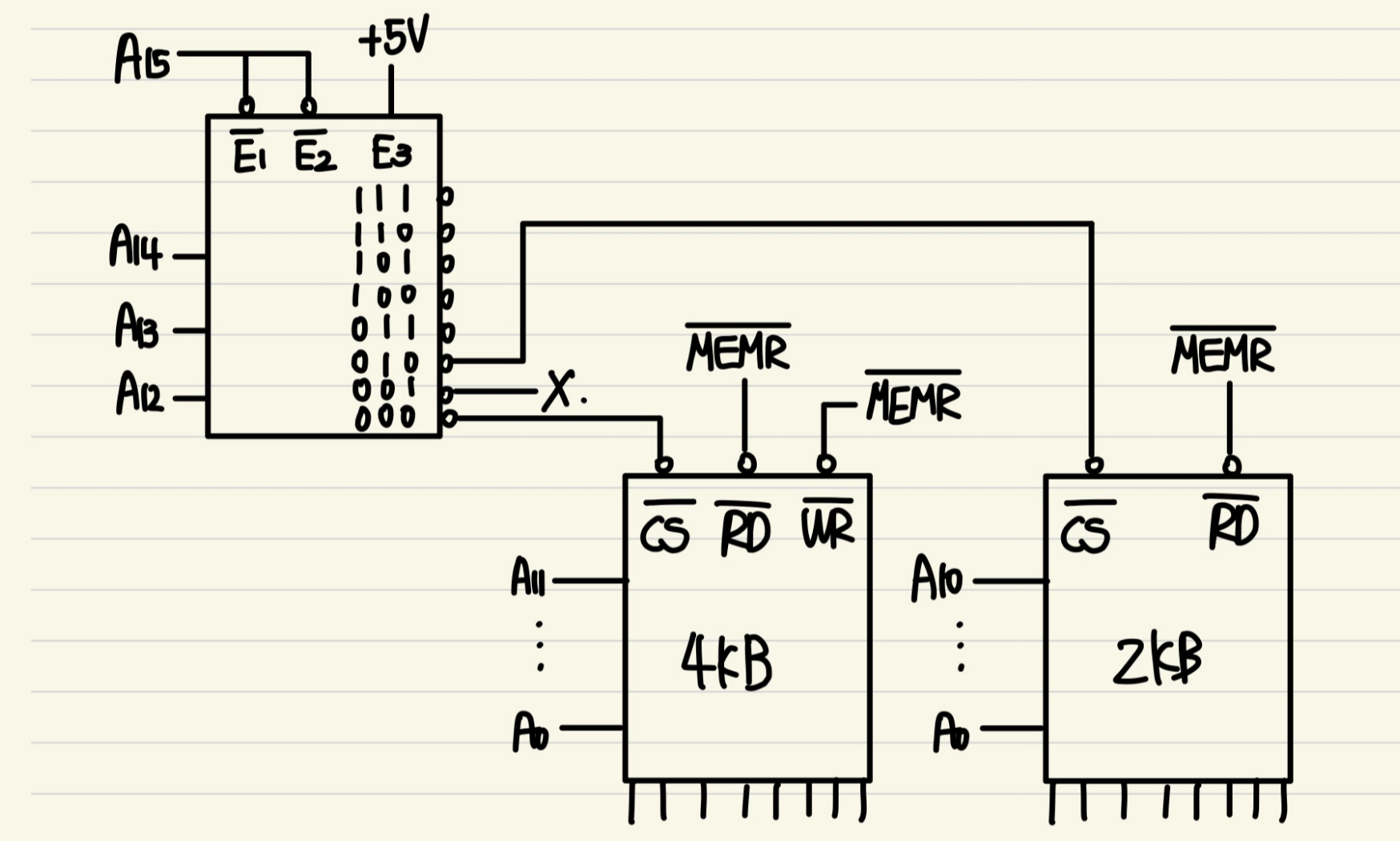

1) 0000H ~ 4kB 짜리 R/W 메모리를 설계하자.

2) ~ 4kB만큼 비워두자.

3) ~ 2kB짜리 ROM을 설계하자.

-> 2kB는 4kB/2이므로, A11까지 address bus에 담지 말고, A10까지만 address bus에 담자.

-> 따라서 ROM에서 A11은 사용하지 않는다.

4) memory map을 그리자.

<예제 4-1>

Mirror memory가 발생하지 않게 바꿔 그려라.

(= parial decoding 말고, complete decoding을 설계해라.)

'KNU_study > 마이크로프로세서' 카테고리의 다른 글

| 마이크로프로세서(12) 어셈블러 명령어 (0) | 2023.04.21 |

|---|---|

| 마이크로프로세서(11) I/O interface (0) | 2023.04.21 |

| 마이크로프로세서(9) partial decoding, absolute decoding (0) | 2023.04.21 |

| 마이크로프로세서(8) memory map (0) | 2023.04.21 |

| 마이크로프로세서(7) computer의 비트 수, 번지 수 늘리기 (0) | 2023.04.21 |