Memory interface에 대한 내용이 궁금하다면 여기를 클릭 !!

1. Review : Memory interface

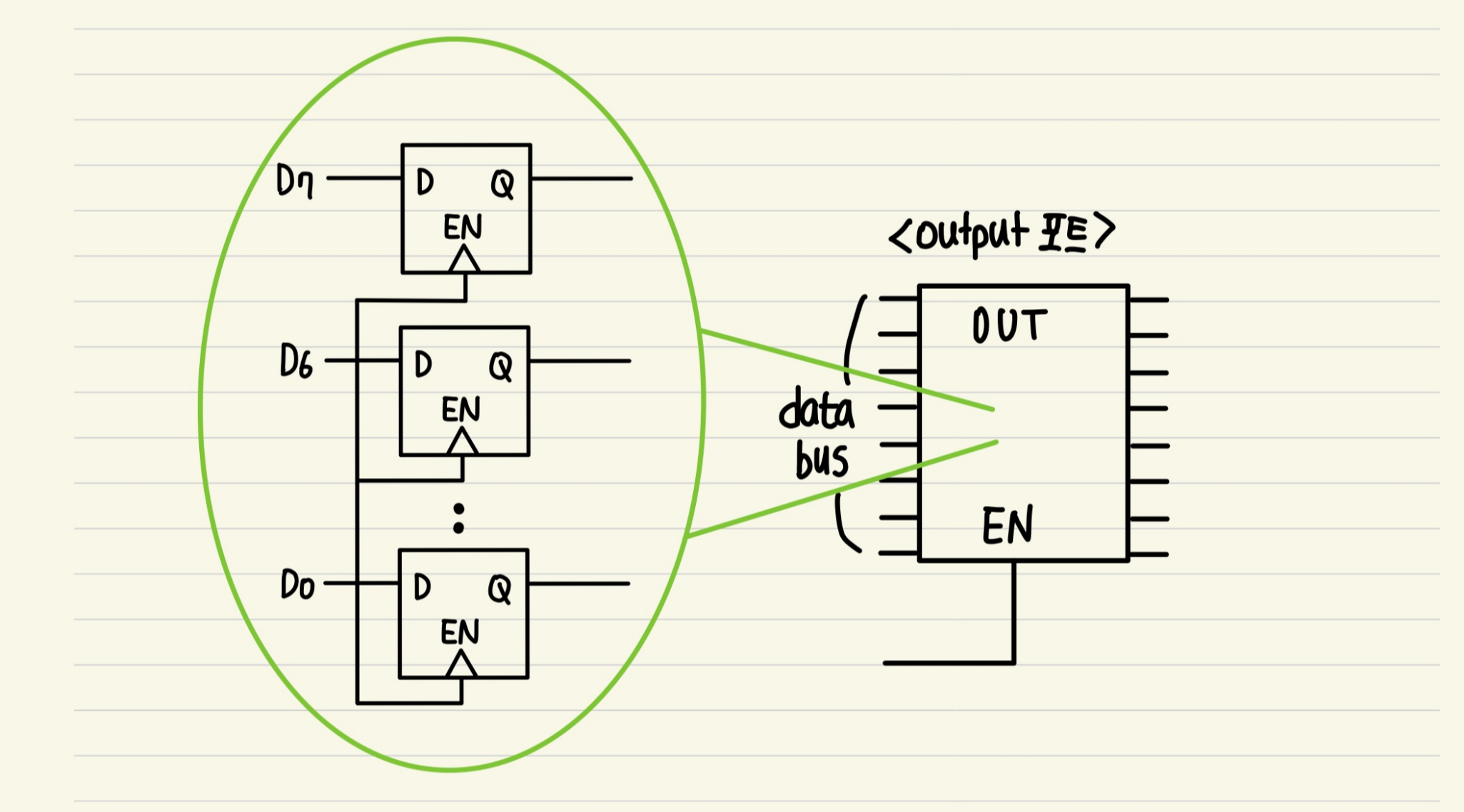

메모리는 D flipflop를 사용한다.

참고로 이번 챕터에서 공부할 I/O는 latch 혹은 버퍼를 사용한다.

2. I/O interface

공간이 모자랄 수 있기 때문에

address bus와 control bus를 결합해서 enable신호를 준다.

-> 둘 다 1일 때만 신호를 흐르게 한다.

3. INPUT 포트와 OUTPUT 포트

<INPUT 포트>

active low로 동작한다.

인풋 포트 00H를 enable시키면 다음 그림과 같다. 그 아래 그림은 비용 절감이라는 장점이 있는 버전이다.

오류 ㅎㅎ ㅠㅠ : input 포트는 NAND 게이트로 연결되어야 함

오류 ㅎㅎ ㅠㅠ : input 포트는 NAND 게이트로 연결되어야 함, 그리고 output이 아니라 input임 ㅠㅠㅠ

-> 주소를 4개 가지는 방법은 다음과 같다.

이런 경우엔 00H, 01H, 02H, 03H를 같이 쓴다.

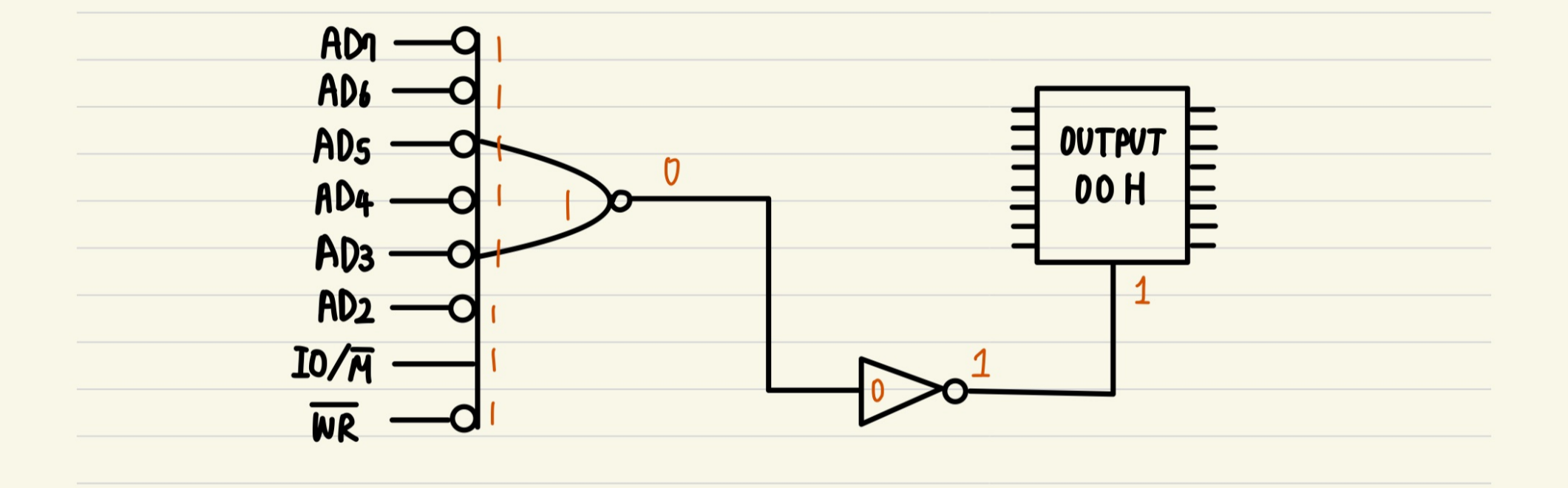

<OUTPUT 포트>

active high로 동작한다.

-> OUTPUT 포트에 관한 기본적인 모델이다.

이걸 쓰면, 28개의 address bus를 사용할 수 있다. --> 너무 많다 !!

그래서 256개의 address bus를 사용하는 대신, control bus를 거기에 사용하자. (아래 그림 참고)

-> 이 버퍼는 00H, 01H, 02H, 03H 4개를 같이 사용한다. address bus를 빼버렸음에도 동작한다.

이를 합치면 다음과 같이 요약할 수 있다. (아래 그림 참고)

-> 마무리로, 예제를 풀어보자. 42H, 52H, 62H, 72H를 같이 사용하는 OUTPUT 포트를 그리시오.

4. 38 decoder로 나타낸 INPUT 포트, OUTPUT 포트

<예제1>

아래의 경우에 어떻게 설계해야 할까?

IN 05H

OUT 06H

-> I/O mapped I/O를 사용하여 설계하자.

<예제2>

아래의 경우에 어떻게 설계해야 할까?

IN FFF0H

OUT FFF1H

-> memory mapped I/O를 사용하여 설계하자.

| result | I/O mapped I/O | Memory mapped I/O |

| 주소 | 8bits | 16bits |

| control | IOR, IOW | MEMR, MEMW |

| 명령어 | IN, OUT | Memory 관련 명령어 (ex) LDA, STA |

'KNU_study > 마이크로프로세서' 카테고리의 다른 글

| 마이크로프로세서(17) Stack과 Subroutine (0) | 2023.04.21 |

|---|---|

| 마이크로프로세서(16) 프로그램 코드 설계 예제 (0) | 2023.04.21 |

| 마이크로프로세서(14) 타이밍도 (1) | 2023.04.21 |

| 마이크로프로세서(13) 어셈블러 명령어2 (0) | 2023.04.21 |

| 마이크로프로세서(12) 어셈블러 명령어 (0) | 2023.04.21 |